# Upgrade of the Jülich Digital Readout System for the Development of the PANDA-MVD

### Motivation

- characterization for the PANDA MVD

- developed in Jülich

- simple adaption to new front end prototypes

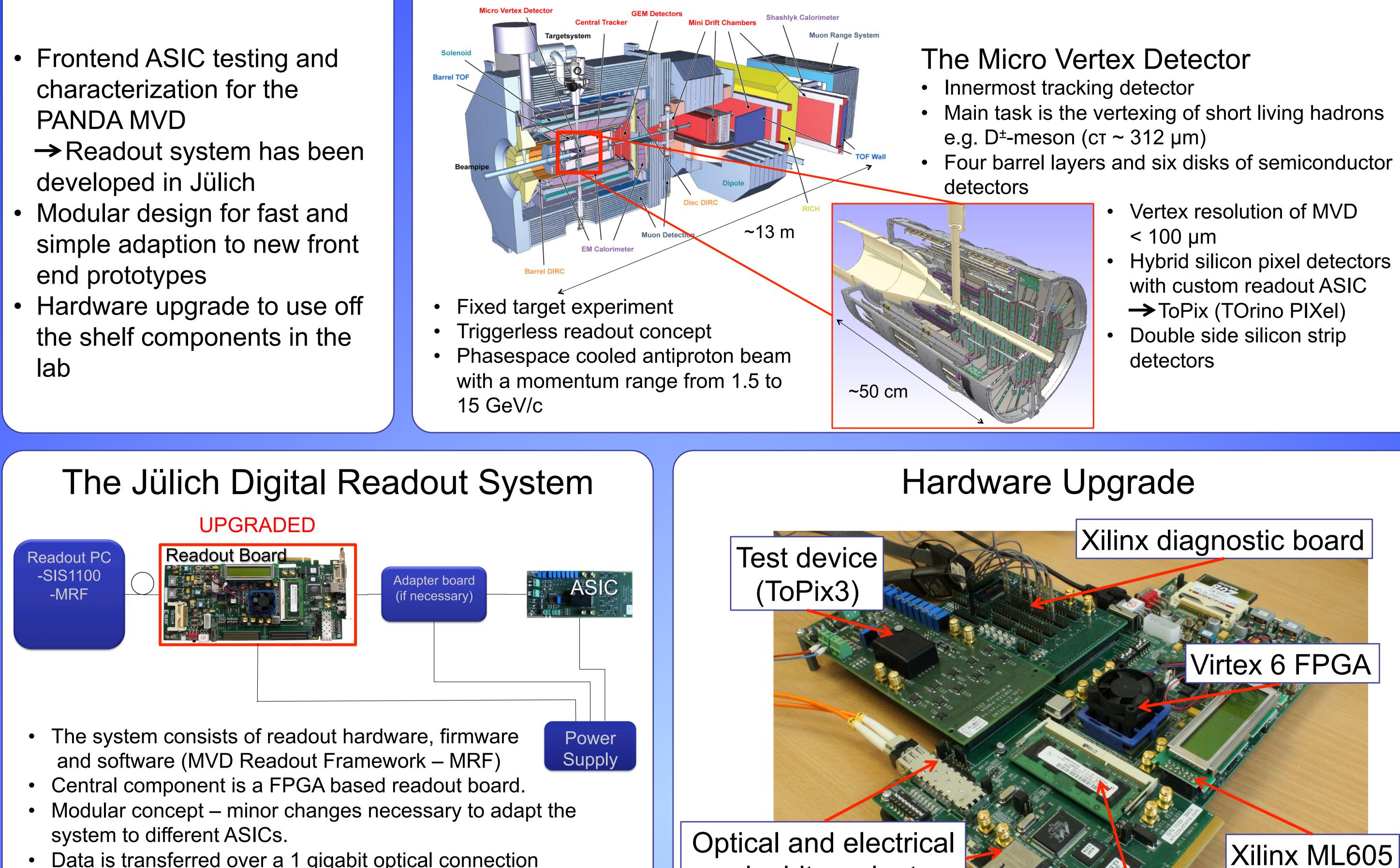

### **The PANDA Detector**

**JÜLICH**

FORSCHUNGSZENTRUM

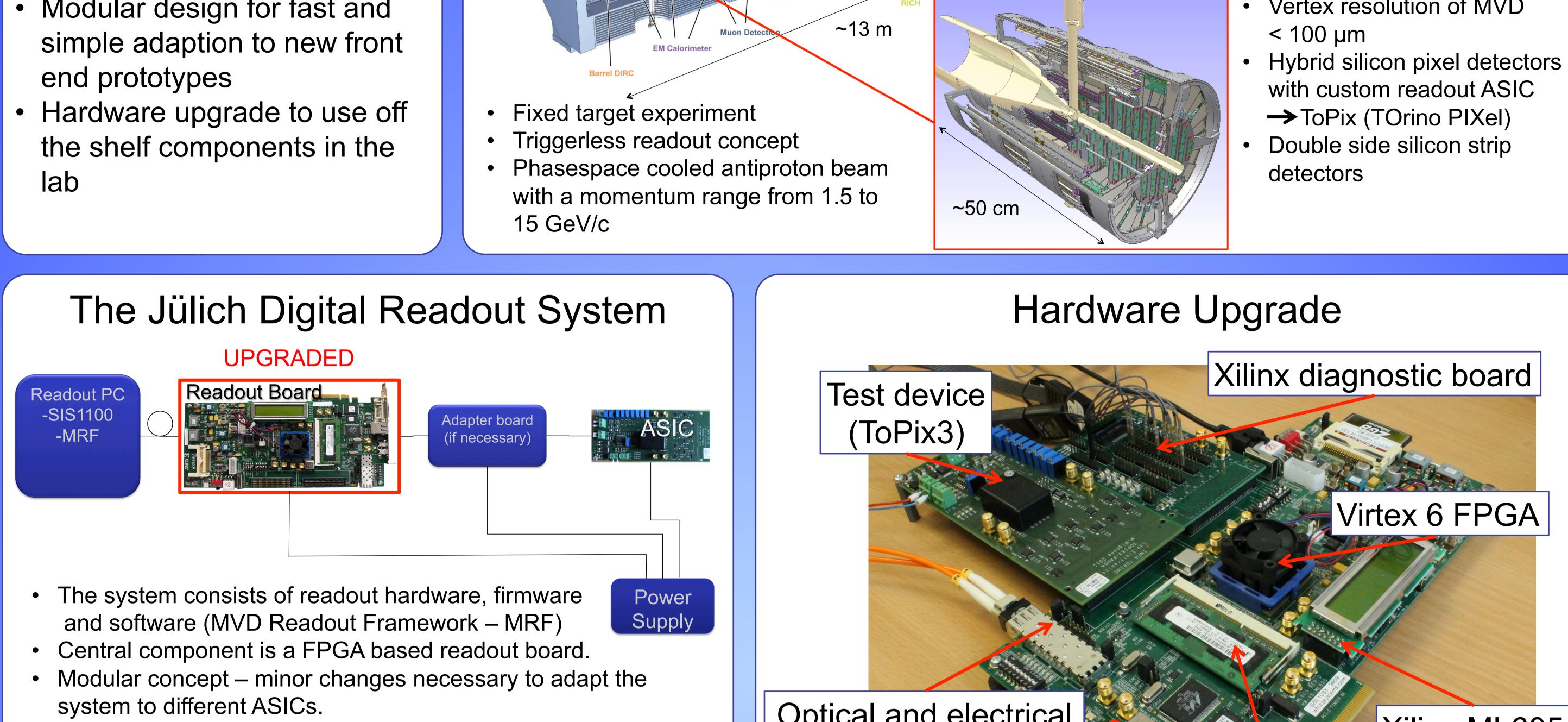

Data is transferred over a 1 gigabit optical connection

**Optical and electrical** gigabit readout

Four communication layers implemented. Every hardware component is treated by a software class (modular design)

**CAL** – Chip access layer **TAL** – Transport access layer **GAL** – Generic access layer

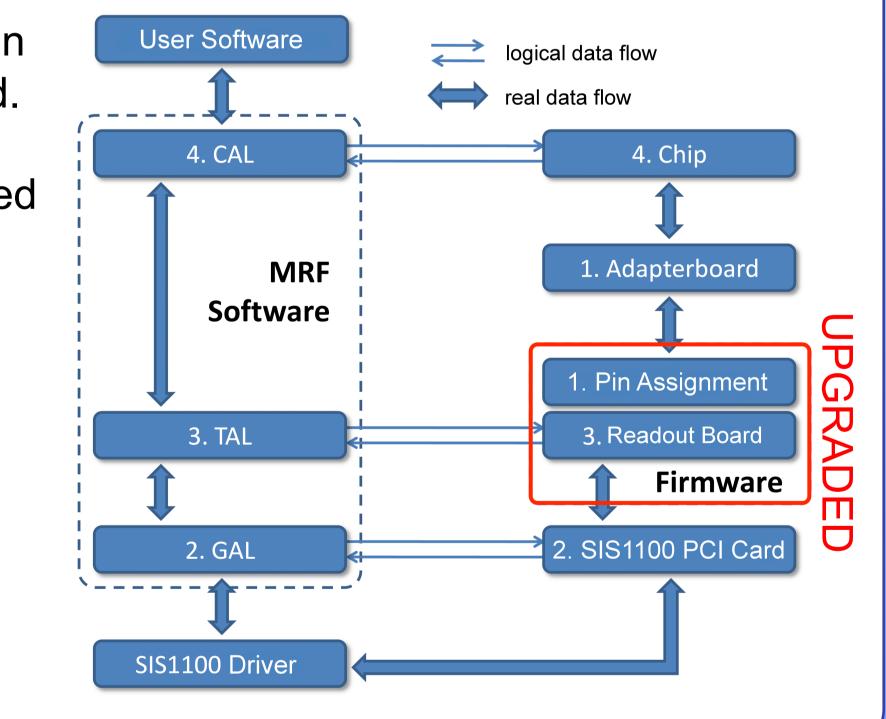

- New central hardware component: Xilinx ML605 Evaluation Board

- Cheap and easy to obtain

- Virtex 6 FPGA

- Expandable DDR3 RAM

- Optical and electrical gigabit connection

- FMC connectors (HPC and LPC)

- LC Display  $\bullet$

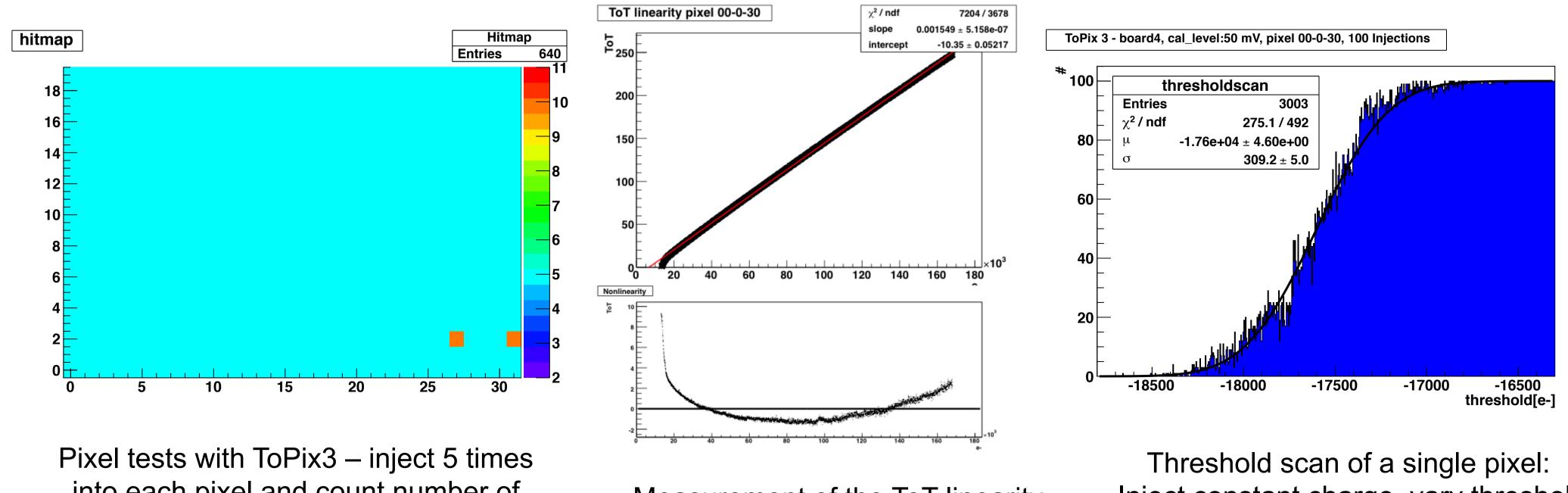

### Measurements with ToPix3

Front end ASIC of pixel part – ToPix. Time over Threshold (ToT) charge measurement.

## Summary

- A readout system exists to characterize front end ASICs

- A hardware upgrade has been developed to extend the

into each pixel and count number of detected hits – two broken pixels found

Measurement of the ToT linearity

Inject constant charge, vary threshold

memory and FPGA resources

- Measurements with the recent ToPix 3 prototype have been done to prove the functionality of the readout system

- Next step: implementation of ethernet based protocol

Simone Esch<sup>1</sup>, Marius C. Mertens<sup>1</sup>, Tobias Stockmanns<sup>1</sup>, Wilhelm Erven<sup>2</sup>, Michael Ramm<sup>2</sup> and James Ritman<sup>1</sup> <sup>1</sup>Institut für Kernphysik, <sup>2</sup>Zentralinstitut für Elektronik

Forschungszentrum Jülich GmbH for the PANDA collaboration