#### The PASTA chip for the silicon micro strip sensor of the PANDA **MVD**

#### Alberto Riccardi<sup>1</sup>

Kai-Thomas Brinkmann<sup>1</sup>, Valentino Di Pietro<sup>1</sup>, Tommaso Quagli<sup>1</sup>, James Ritman<sup>2</sup>, Angelo Rivetti<sup>3</sup>, Manuel Rolo<sup>3</sup>, Robert Schnell<sup>1</sup>, Tobias Stockmanns<sup>2</sup>, André Zambanini<sup>2</sup>, and Hans-Georg Zaunick<sup>1</sup>

- 1) II. Physikalisches Institut Justus-Liebig-Universität Giessen

- 2) Forschungszentrum Jülich

- 3) INFN Sezione di Torino

II. Physikalisches Institut

DPG Spring Meeting 2016

### Contents

- 1. Context

- 2. ASIC design

- 3. Current status

- 4. Outlook

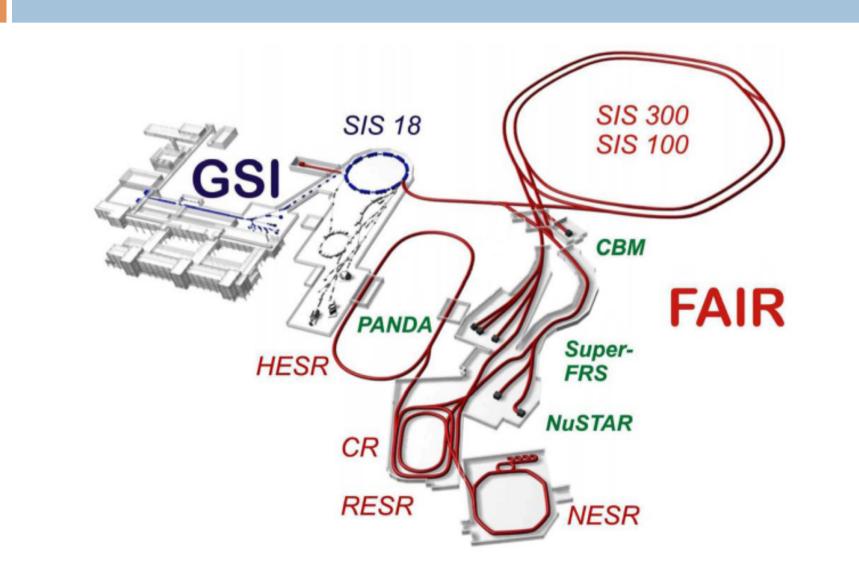

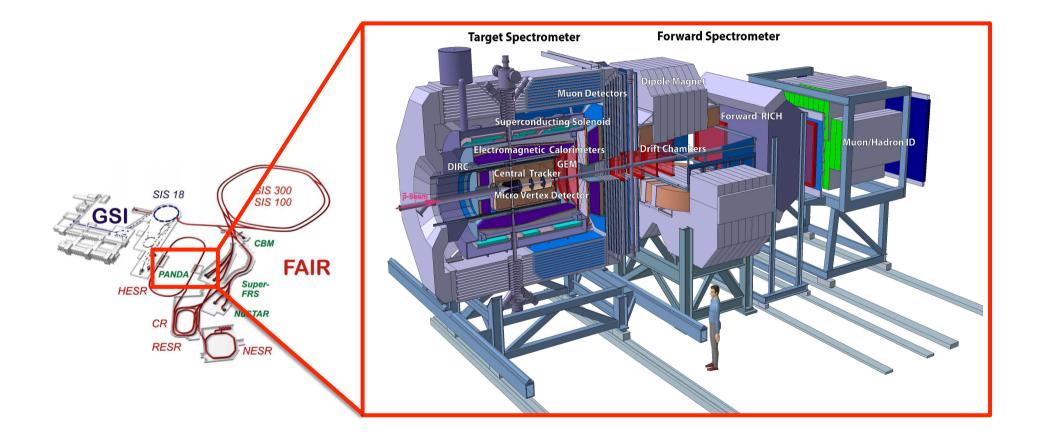

#### PANDA

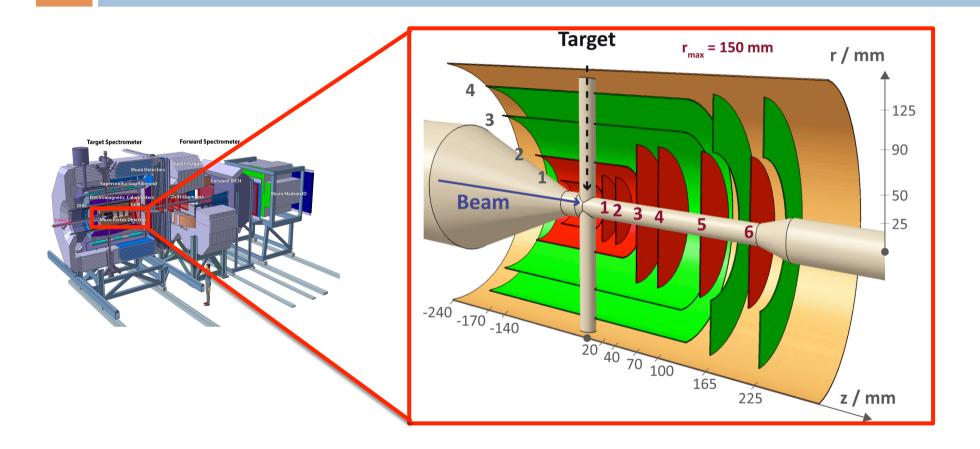

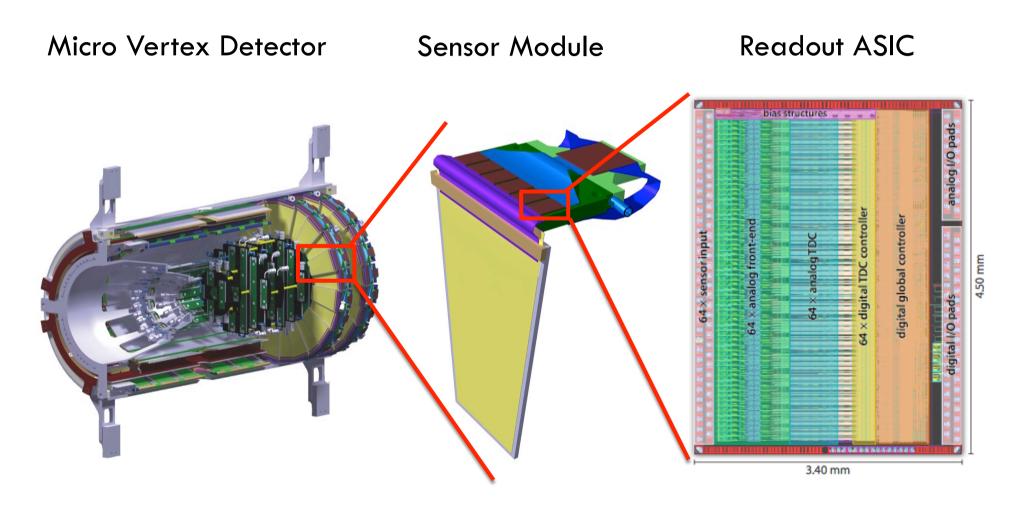

### **MicroVertex Detector**

Red zone covered by pixels and green one by strips

# PAnda STrip Asic (PASTA)

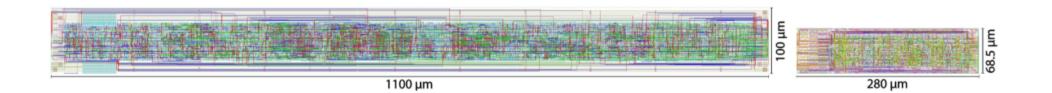

### **PASTA Features**

- 64 Channels

- $\Box$  63  $\mu$ m input pitch

- 100 kHz Rate/channel

- □ Less then 4 mW per channel

- □ Triggerless

- Radiation tolerance 100 kGy

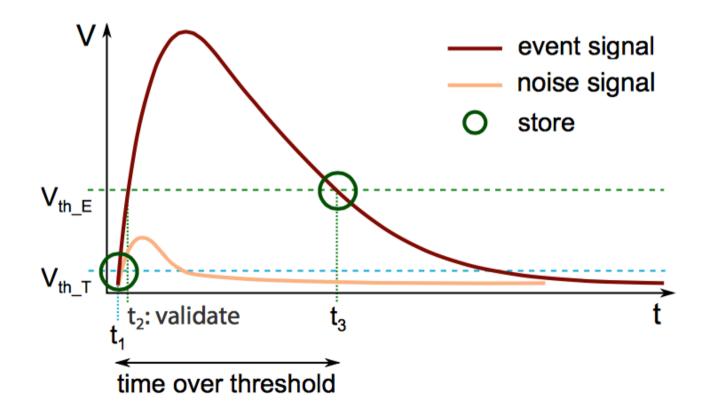

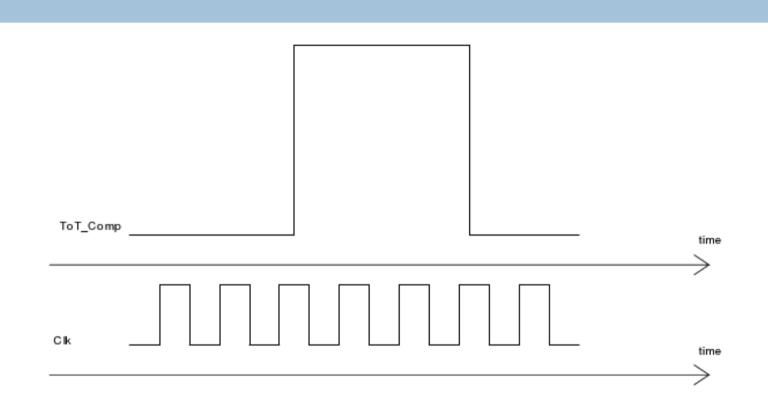

#### Measurement Concept

- Low threshold: better time stamp resolution

- High threshold: better jitter performance

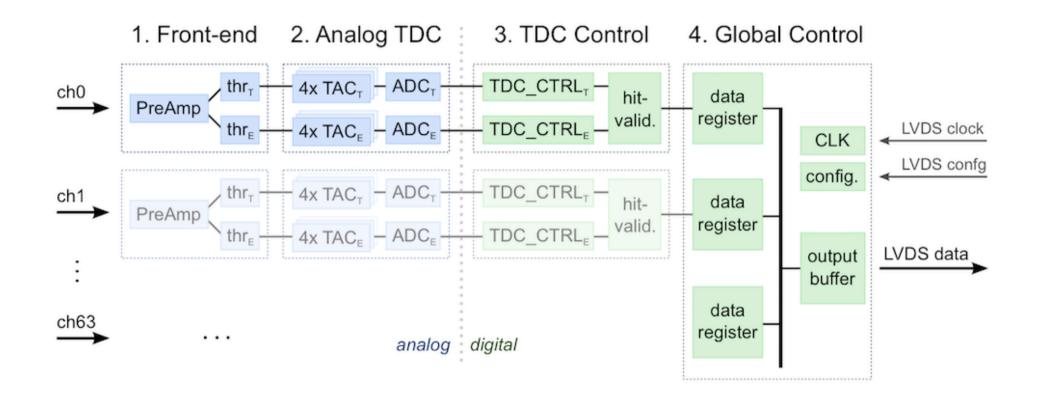

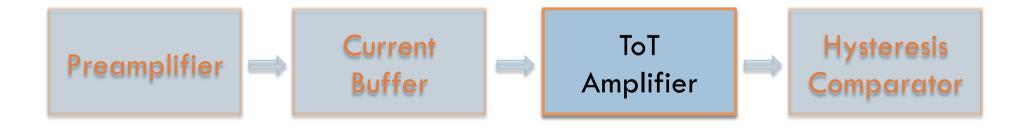

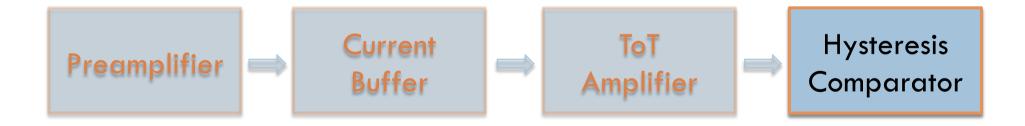

### **PASTA Architecture**

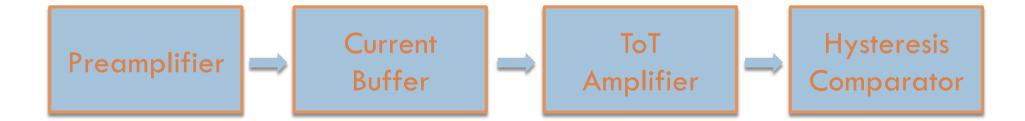

- First preamplification

- Two input polarities, same output polarity

- Current amplification

- Impedance adapter

- Last amplification

- Constant current discharge of feedback capacitance

- Low noise sensitivity

- Two for each channel : energy and time branches

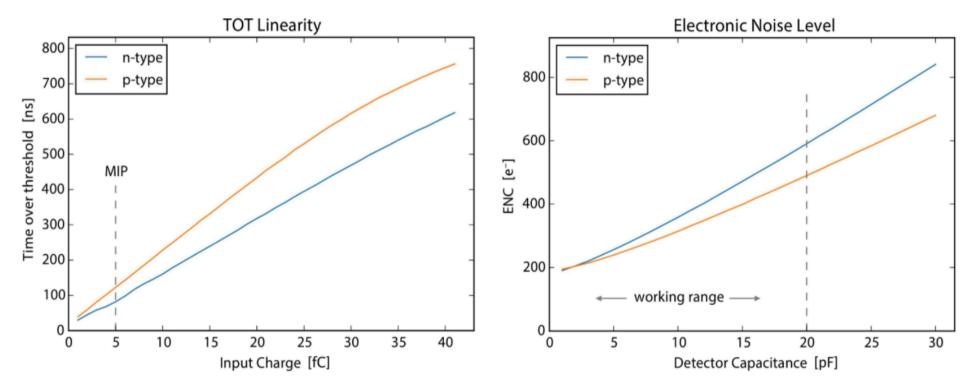

## **Front-End Simulations**

ToT linearity in the input charge range of 1fC to 40 fC with a capacitance of 25 pF Electronic noise considering an input capacitance in the range 1pF to 30 pF with an input charge of 4fC

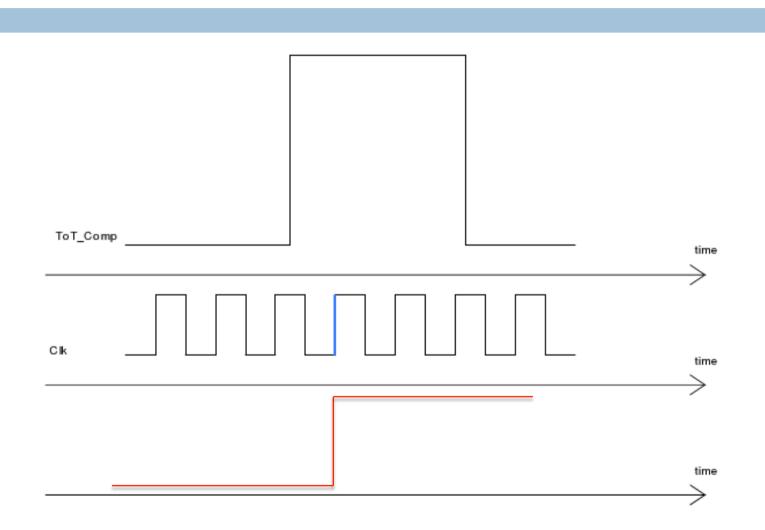

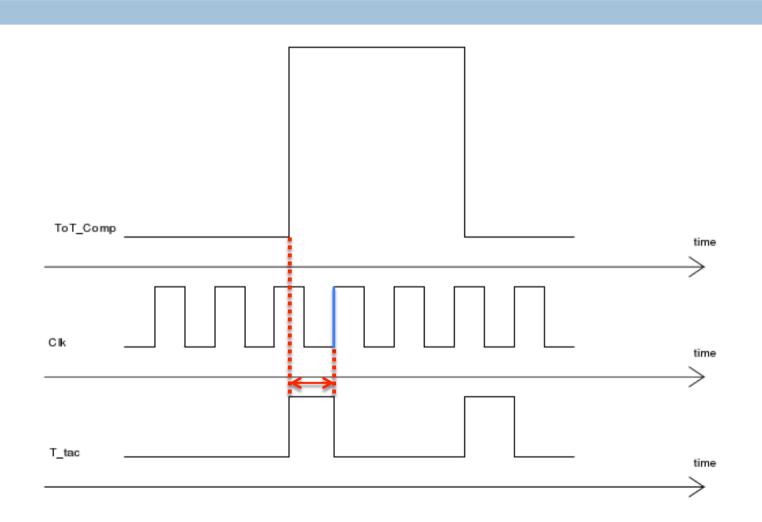

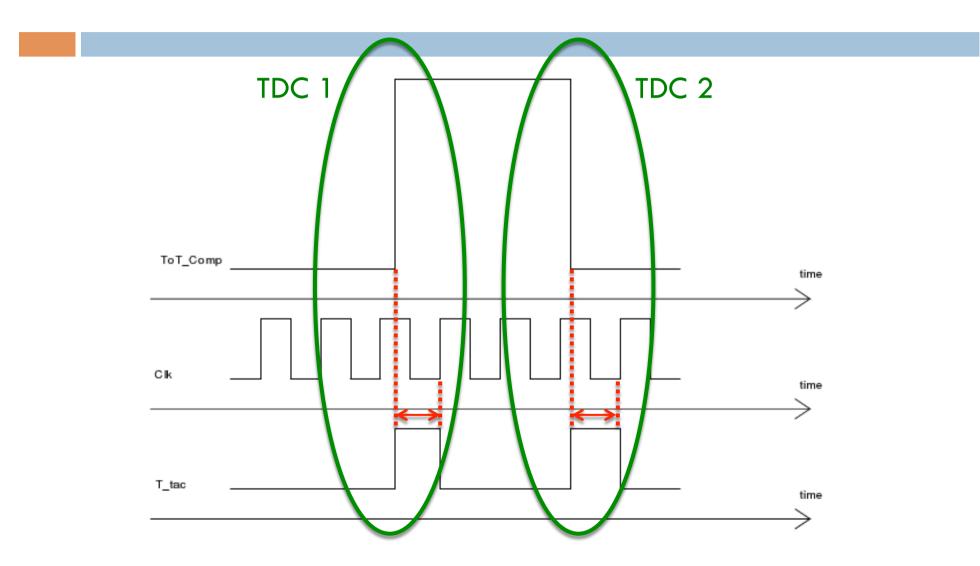

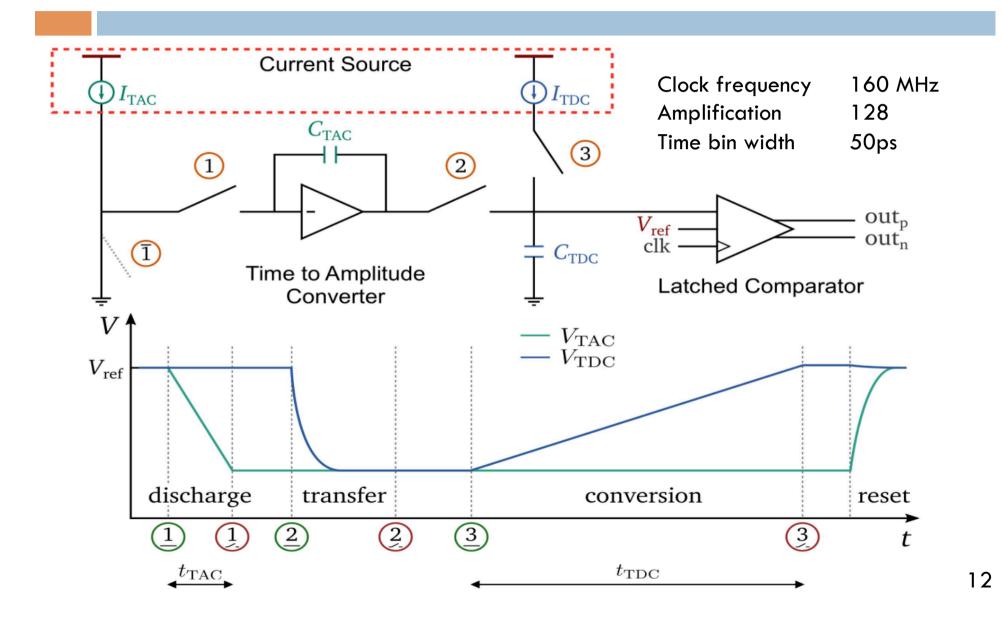

## **Analog TDC Performance**

# **Digital Controllers**

#### Optimization of the TDC Controller

- Size reduced by 80%

- Overall power consumption halved

- Radiation-hard logic implemented

- Single Event Upset protection

- 1 bit : TripleModular redundancy

- n bits : Hamming encoding

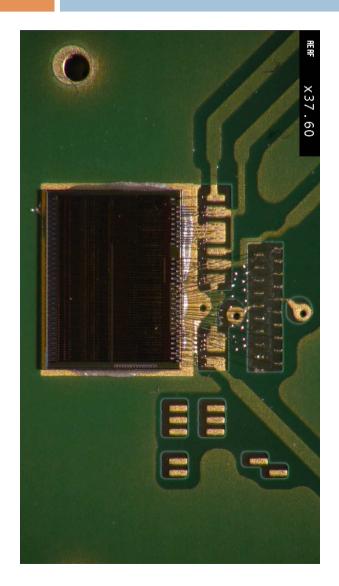

## **Current Status**

- Chip bonded to the power board

- Power supplies tested

- Readout system under test

## Outlook

□ Board in production

□ First tests scheduled

Beam test with sensor planned in the middle of the year

Alberto Riccardi

Alberto.Riccardi@exp2.physik.uni-giessen.de

# Thank you for your attention

GEFÖRDERT VOM

Bundesministerium für Bildung und Forschung

II. Physikalisches Institut