## From Cesar Prados (GSI, Darmstadt)

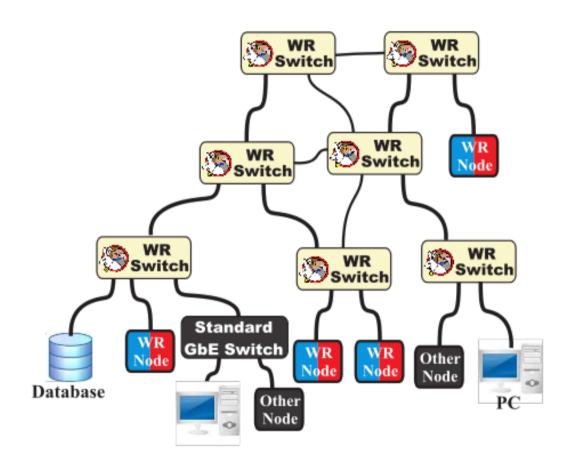

- Few thousands nodes

- Copper or fiber medium

- Up to 10 km fiber links

- Bandwidth: 1 Gbps

- WR Switch: 18 ports

- Non-WR Devices

- Ethernet features (VLAN)

& protocols (SNMP)

1

## From Cesar Prados (GSI, Darmstadt)

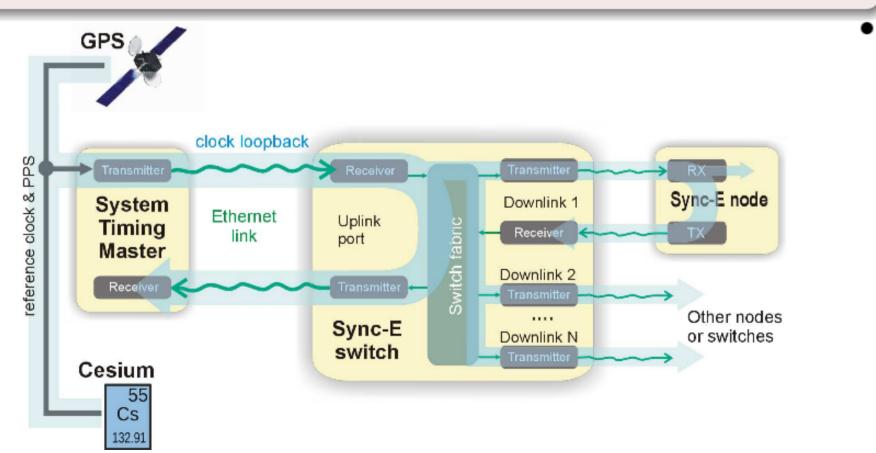

#### Common clock for the entire network

- All network devices use the same physical layer clock

- Clock is encoded in the Ethernet carrier and recovered by the receiver chip (PHY).

2

## From Cesar Prados (GSI, Darmstadt)

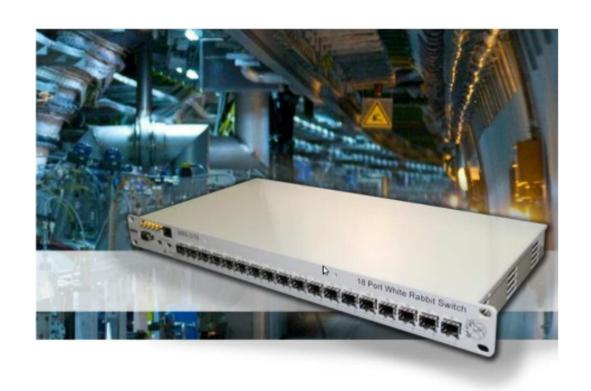

- Central element of WR network

- Original design optimized for timing, designed from scratch

- 18 1000BASE-BX10 ports

- Capable of driving 10 km of SM fiber

- Open design (H/W and S/W)

3 De Remigis

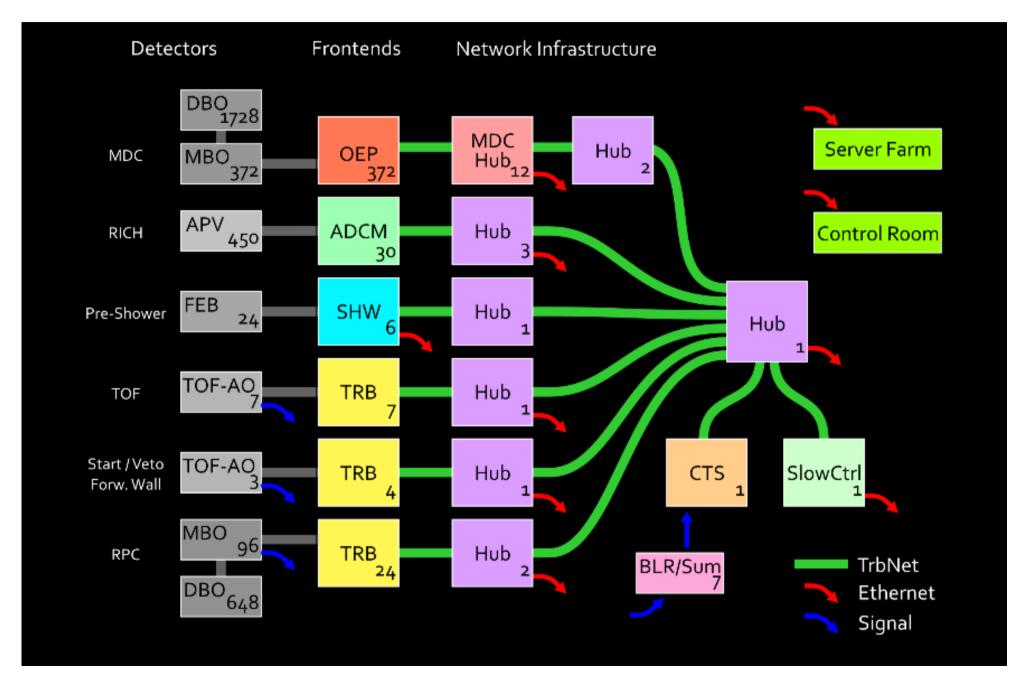

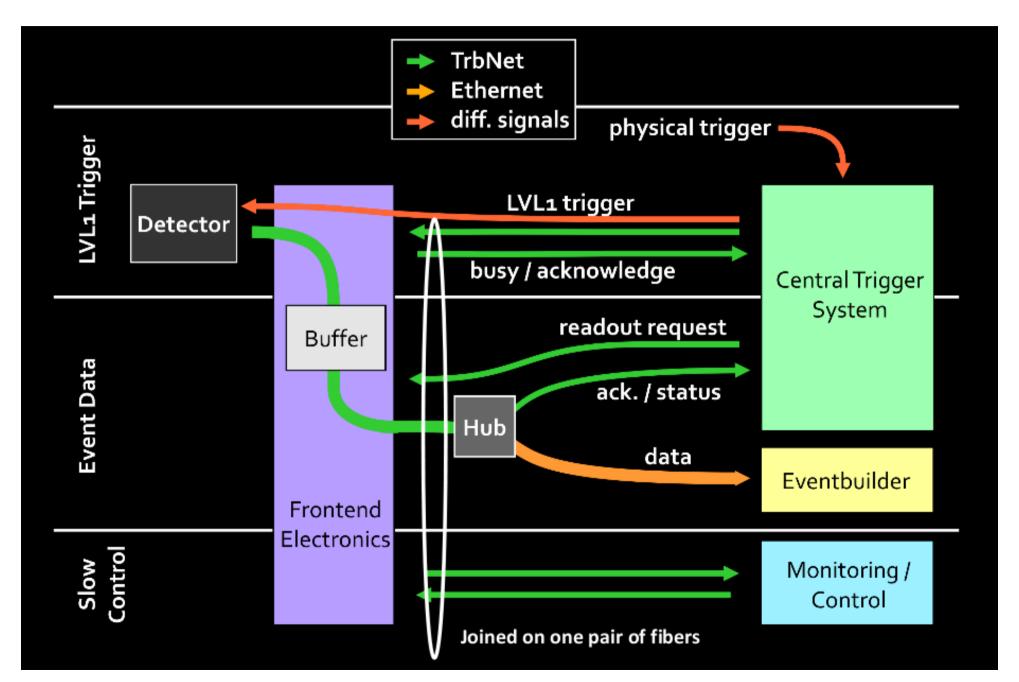

# From Jan Michel (University, Frankfurt)

4 De Remigis

# From Jan Michel (University, Frankfurt)

5

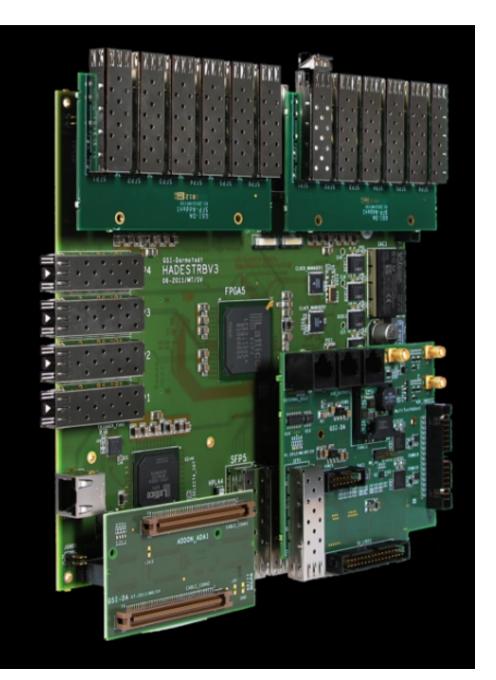

# From Jan Michel (University, Frankfurt)

- Multi-purpose FPGA platform

- Extension via AddOn-Boards

- 200 I/O per FPGA

- Up to 32 x 3.2 GBit/s (with AddOn)

- Full control via GbE

- · Stand-alone operation

- · Read-out via GbE

- Internal trigger system

- Logic for coincidences, delays, spike suppression, random and regular pulsers...

- In cooperation with

- PANDA-DIRC (GSI / Univ. Mainz)

- PANDA-STT (Univ. Krakow)

- And many others

• The flow of the Synchronization Of Data Acquisition (Soda) will be unidirectional, from the source to the front end.

• The slow control will be transported by the same network of the Soda timing, but it will not be part of Soda protocol.

A large commercial switch with the Infiniband technology will be evaluated, as an alternative to the Compute Nodes.

The responsibilities for the Soda source has been assigned to KVI (Lemmens) and Krakow, and Frankfurt.

• Within February the compatibility of the TRB.net, with the requirements on the accuracy and jitter, will be verified.

• The implementation of the Soda.net hardware, for the STT and Dirc, will be responsibility of Krakow (Palka).

• The implementation of the Soda.net hardware, for the MVD (pixel and strip), will be responsibility of FJ (Kleines).

• In November a test for the prototypes of the Soda hardware with the detectors is foreseen, at FJ or GSI.