# TDC and Read out Board version 3

# Marcin KAJETANOWICZ Jagiellonian University

- TRB version 2

- TRB version 3

- Specification

- Layout

- Application

- Current status

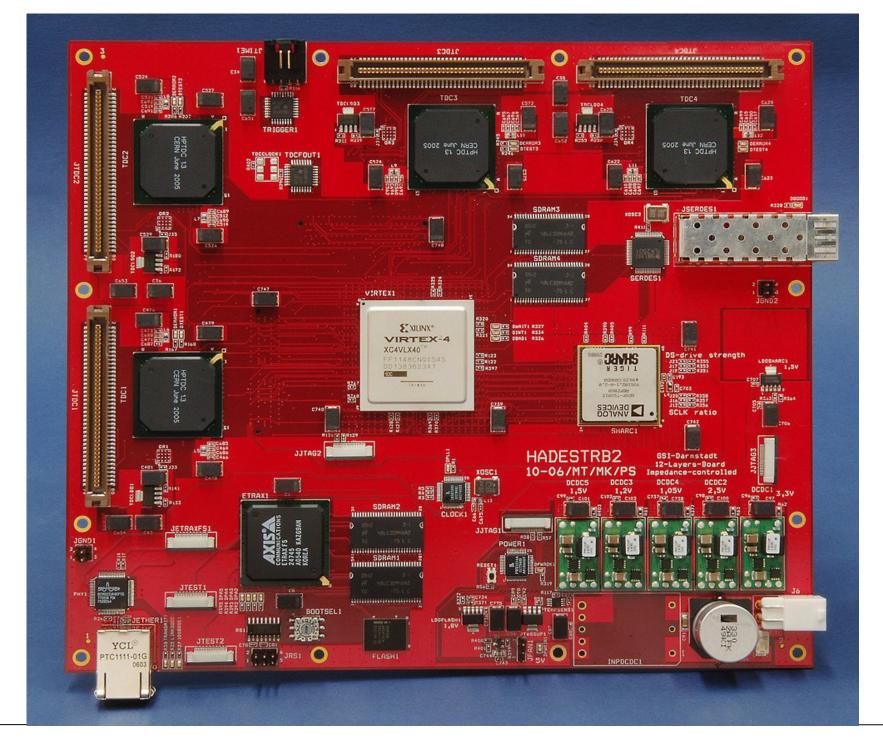

# TRB version 2

- 4 x HPTDC

- Viretx 4

- DSP (Sharc from Analog Devices)

- ETRAX FS with Linux

- SDRAM (32M x 32-bit)

- 100 Mb Ethernet

- 2.5 Gb/s optical link

Kraków, 26 – 27 April 2011

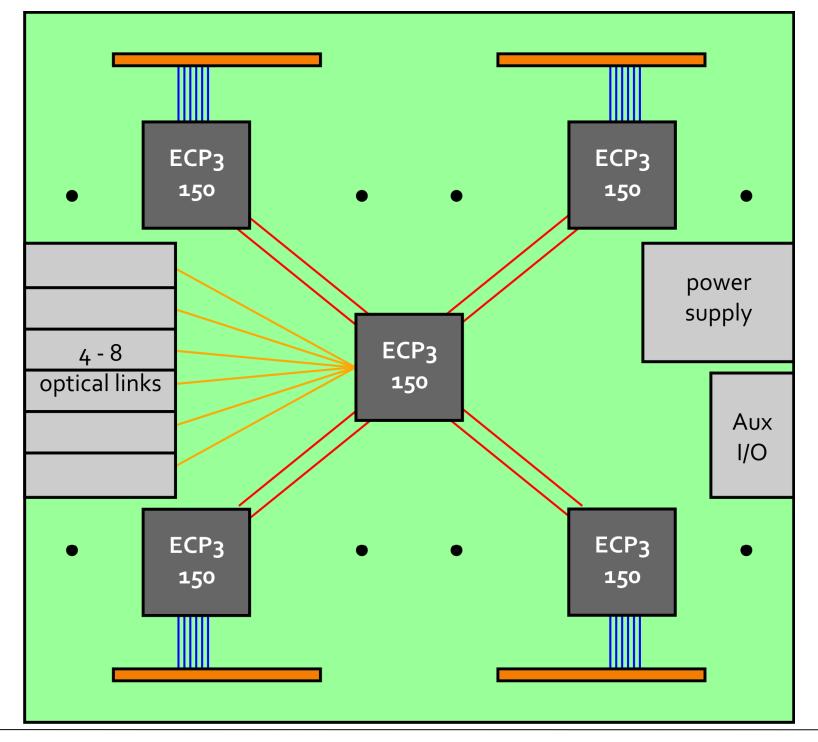

## TRB version 3

- ECP3 FPGA family from Lattice

- LFE3-150EA-8FN1156C central FPGA

- LFE3-150EA-8FN672C edge FPGA

- 4 to 8 3.2 Gb/s optical links

- 4 208-pin I/O connectors

- 125 MHz and 200 MHz on-board oscillators

- External trigger and clock inputs

- Single 48 VDC power supply

Kraków, 26 – 27 April 2011

## Mezzanine card connector

#### QMS family from Samtec

#### **Performance:**

Pins: up to 8.0 GHz / 16 Gbps

Supply blades: max. current: 9.2 A

#### Pin usage:

12-bit DQ lanes 13

2.5V lines 16

bidirectional serdes lines 6

2.5V lines from central FPGA 8

3.3V lines from central FPGA 4

four supply blades: 2 \* GND, +6.5V, +3.3V

# Mazzanine Card

- Edge FPGA has six serial, high speed links to the connector and 164 digital data lines

- Supply voltages: 6.5V and 3.3V

#### Applications:

- Adapter for a cable connection

- Optical data transmitter

- Multichannel ADC card

# TRBv3 Application

- Each edge FPGA may contain up to 40 TDCs

- Time resolution confirmed by tests: <10 ps</li>

- Edge FPGA has two high speed links to the central FPGA (up to 3.2 Gb/s)

- Central FPGA may have up to eight optical links

# Status

The design complete

PCB design in progress (mid-May)

Production mid-June

From June on → tests

Code development is going on