# SODA: Synchronization Of Data Acquisition I.Konorov

➢ Requirements

>Architecture

System components

> Performance

Conclusions and outlook

23.04.2009

PANDA FE-DAQ workshop Bodenmais

Igor Konorov

### **Requirements & Functions**

### Requirements

Provision of absolute time at Front-end electronics Precision 20 ps for ToF and >50 ps for all other detectors Synchronization with operation of HESR Synchronization with Target

Implementation :

Time reference

single clock to all front-ends via optical network – 125MHz (100-155.52) Absolute Time

- RESET SIGNAL

- sets local time counters to ZERO

- issued at start of run

Start/End of data block

Heart Bit – Start of Block/End Of Block signals

HESR beam structure : 2us beam & 400 ns no beam

Enable/Disable Data

data throttling

### Extra functions :

Data flow control calibration, tests ....

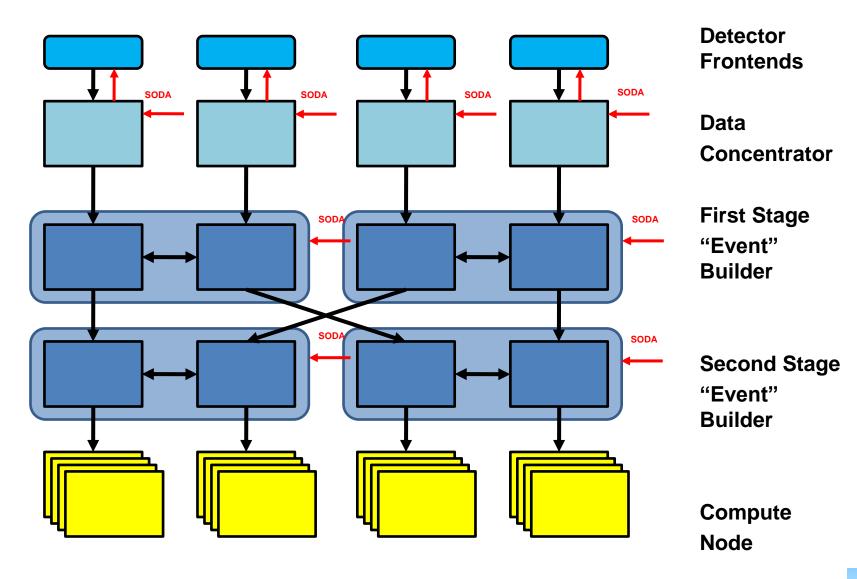

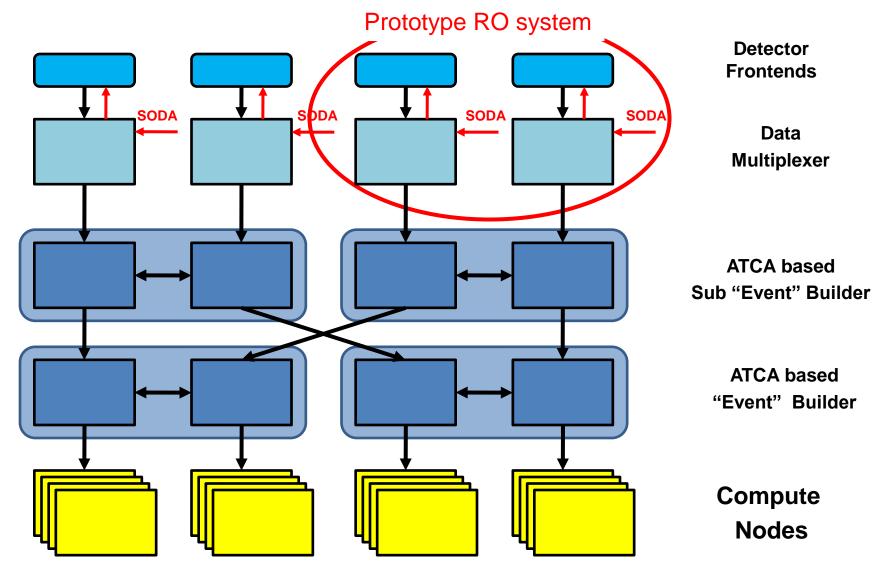

## **DAQ** Architecture

## **SODA** architecture

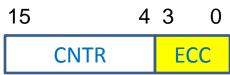

CNTR bits - START, STOP, RESET, Burst START, Burst STOP, Calibration Pulse,...

### Asynchronous, high priority

DATA - Time Tag 40 bits, 2 hours of data taking

### Asynchronous, low priority

4095 O DATA type DATA

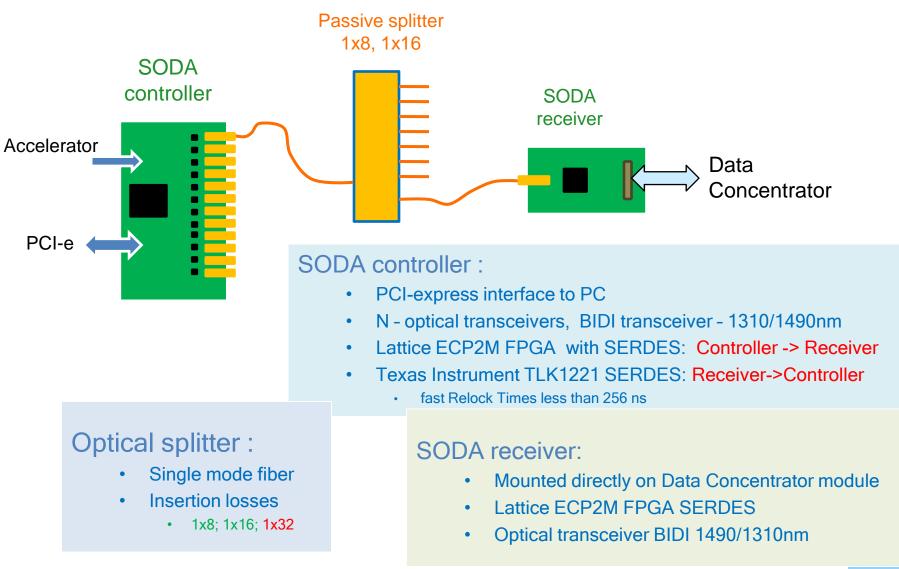

# SODA serial interface

- 125 MHz or 1.25 Gb/s now, in future may go up to 2.5Gb/s

- Bidirectional link :

0 8

- Controller -> Receivers full bandwidth of 125 MB/s

- Broadcast synchronous commands with fixed latency, 32 bit long:

- RESET, Start/Stop data taking, Start/End of burst

- Asynchronous commands , 32 bit long

- Scanning connected modules

- Control

- Packets up to 1kB

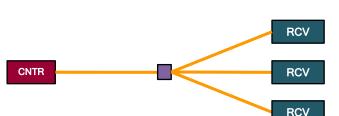

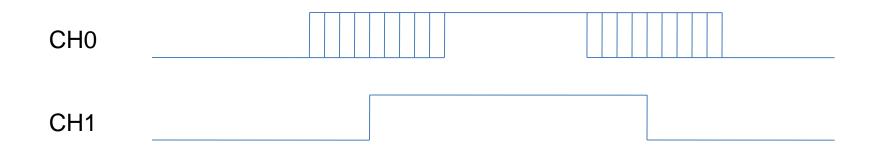

- Receivers -> Controller

- Time sharing principle, similar to common bus

- Only one receiver can send data at a time

- Controller schedules Receivers access

- Switching from one receiver to another takes 400 ns

- Laser OFF Laser On Relock SERDES to new receiver

- Heartbeat packet

- Status packet

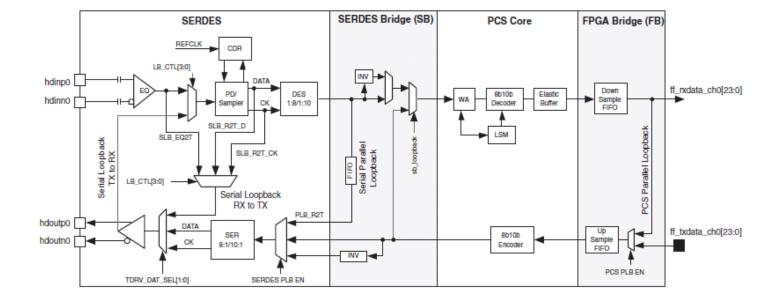

# FPGA SERDES, Lattice ECP2M

Two clocks domain

Igor Konorov

### FPGA's SERDES locking sequence

- Locking CLOCK

- Lock byte boundaries

Recovered clock jitter = one period

Solution:

- Use two Deserializes + FPGA based TDC

- First deserialize reference

- Second reset second RX until Latency is minimum

## **SODA Receiver**

PANDA FE-DAQ workshop Bodenmais

Igor Konorov

# **SODA Receiver connector**

- 125 MHz CLK , LVDS

- High speed serial link

- JTAG interface SODA Receiver Master

- JTAG interface Carrier card Master

- 16 LVDS line for debugging and user reqiurements

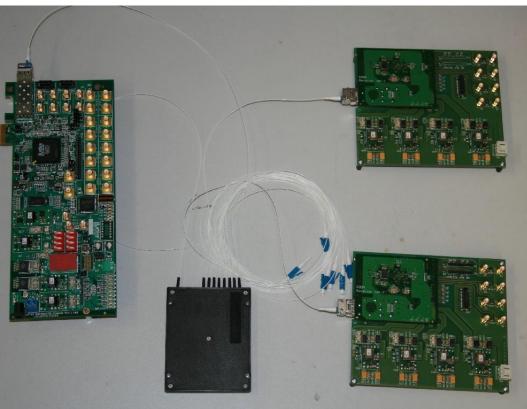

## Test setup

Lattice PCI-e evaluation card Optical splitter 1:8 2x SODA receivers mounted on evaluation cards

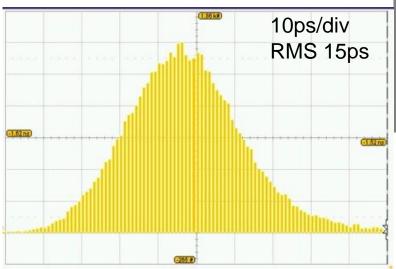

### Reference Clock vs Recovered Rx Clock

## SODA controller and receiver

Lattice SC PCIe evaluation card - SODA controller prototype

SODA receiver AMC card Lattice ECP2M35 256FBGA To be delivered this week

## **Conclusions and outlook**

- System components been validated

- FPGA SERDES validated clock jitter < 20 ps</li>

- Fibre transceivers

- Passive optical splitters

- Next step

- Implement data transmission protocols with minimum functionality

- Develop new optical splitter with asymmetrical insertion losses

- Define first application !!

# DAQ Architecture

Igor Konorov**FutureDAQ**

23.04.2009